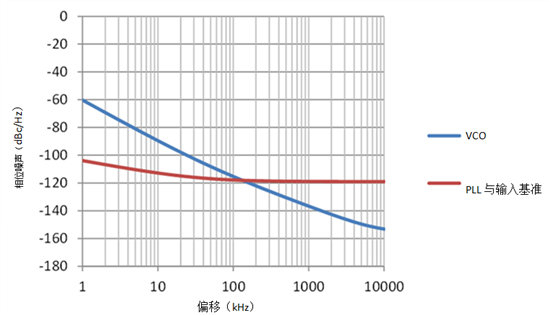

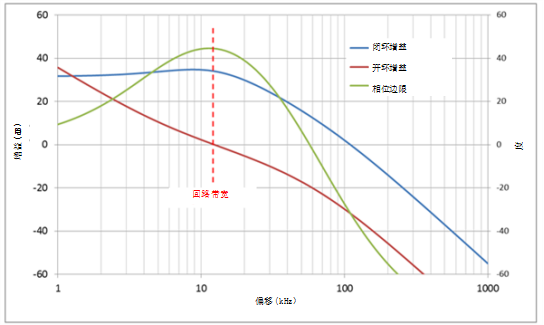

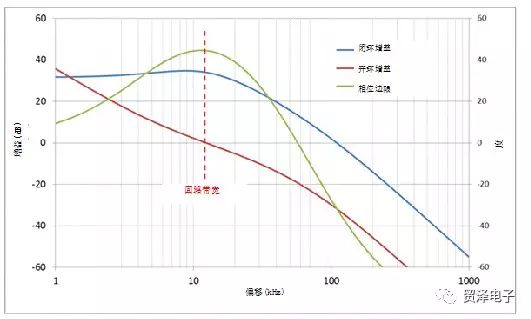

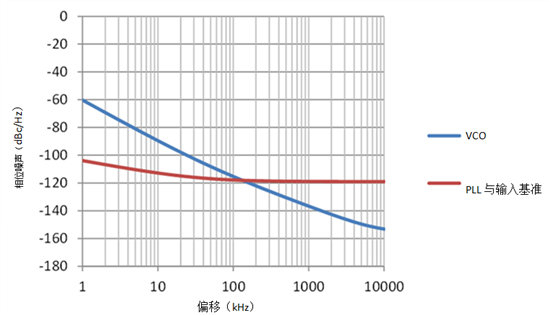

本篇文章是关于相位锁定环(PLL)频率合成器的设计和分析,重点讨论了相位噪声和频率噪声的测量、建模和仿真方法。文章以设计一个假想的PLL频率合成器为例,详细介绍了设计过程和步骤。从规格选择、电路配置

2023-10-26 15:30:51 483

483

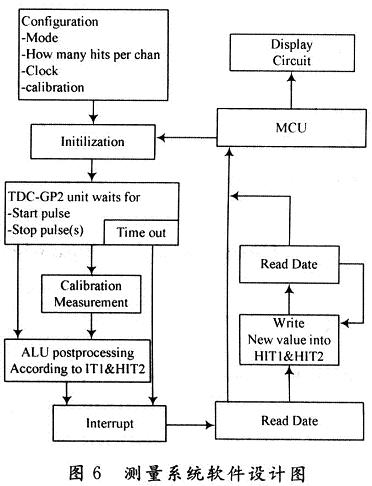

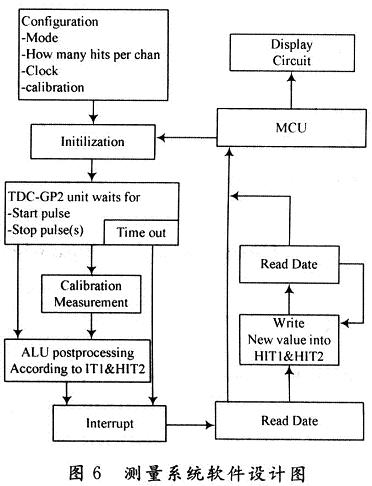

真实测量精度是随机误差和系统误差的函数。随机误差是分辨率不确定度的来源,它包括量化误差(在闸门时间窗内围绕最终计数的不确定度),触发误差(如在噪声尖峰上触发)和时基的短

2011-10-24 14:55:50 5997

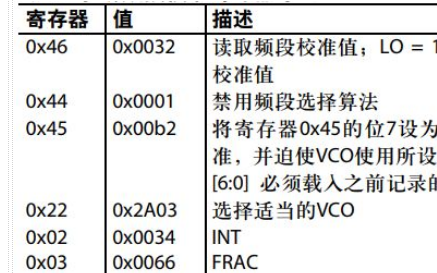

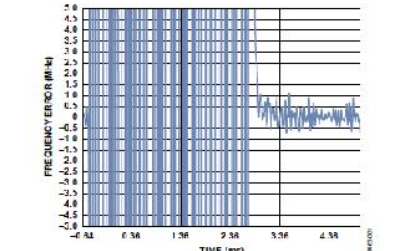

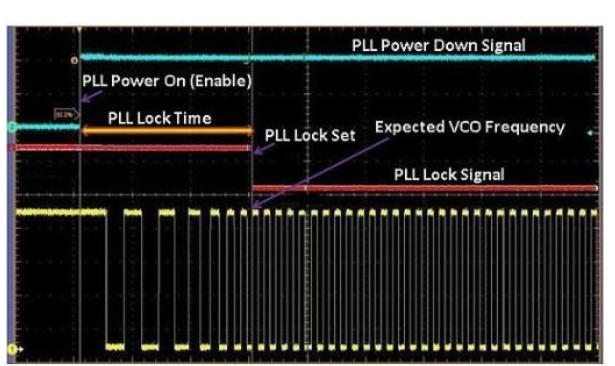

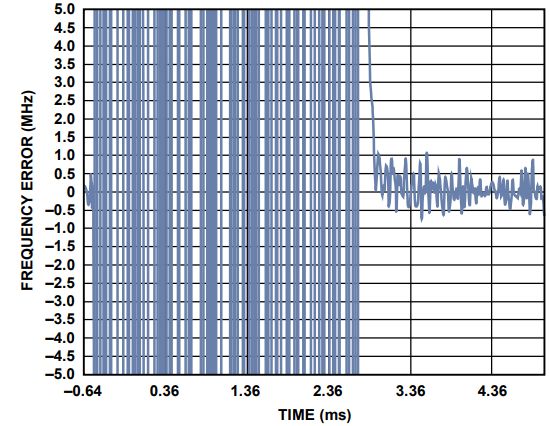

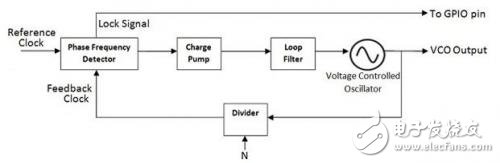

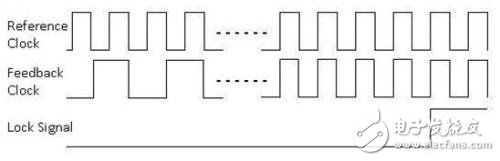

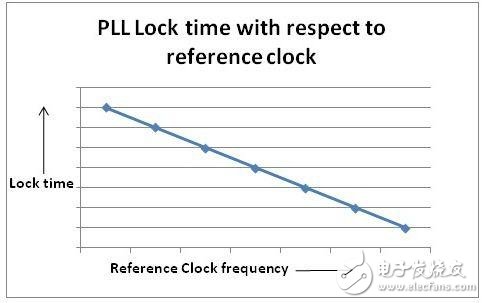

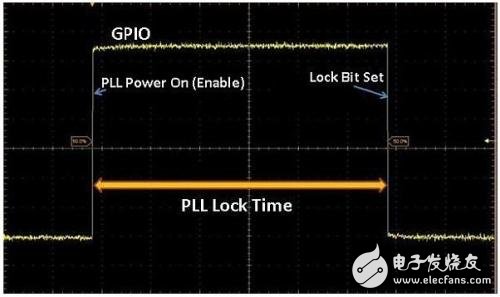

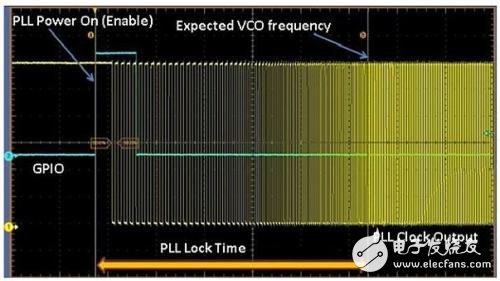

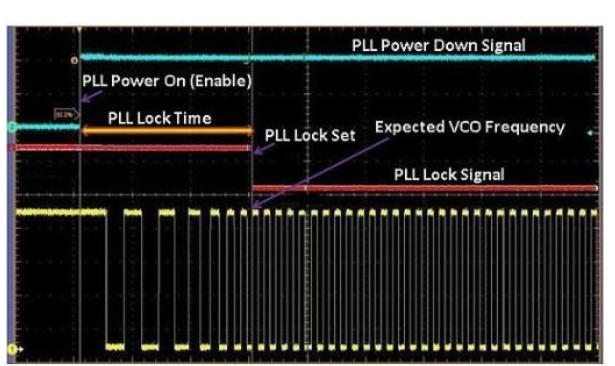

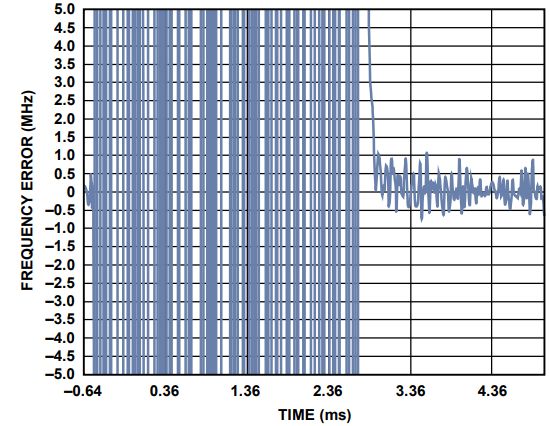

5997 按照上述步骤校准完成后,PLL 的反馈操作使 VCO 锁定于正确的频率。锁定速度取决于非线性周跳行为。PLL总锁定时间包括两个部分:VCO频段校准时间和PLL周跳时间。VCO频段校准时间仅取决于PFD频率;PFD频率越高,锁定时间越短。

2018-05-18 08:35:20 5327

5327

本文以高度集成的解调器和频率合成器 ADRF6820 为例,告诉大家如何手动选择频段以缩短PLL锁定时间。

2018-05-22 09:00:04 4813

4813

使用自动校准模式时,总锁定时间对某些应用来说可能太长。 本应用笔记提出一种通过手动选择频段来显著缩短锁定时间的方案

2021-06-21 09:53:59 4651

4651

PLL锁定指示电路该如何设计?

2019-07-30 07:40:35

你知道吗?利用手动频段选择,锁定时间可从典型值 4.5 ms 缩短到典型值 360 μs。本文以高度集成的解调器和频率合成器 ADRF6820 为例,告诉大家如何手动选择频段以缩短PLL锁定时间

2018-11-01 10:42:37

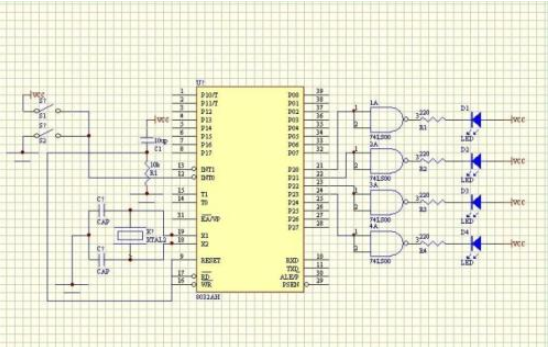

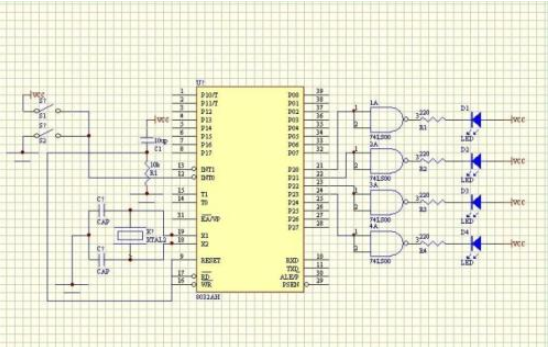

做个双积分ADC,对被测信号进行20ms固定时间积分,然后切换到基准信号通道,测量反向积分时间。固定时间积分用的是T0定时器,测量方向积分时间用的也是T0定时器。现在是在切换到基准信号通道前将TL0

2019-07-01 04:35:16

你知道测量PLL锁定时间的方法有哪几种吗?

2021-05-10 07:11:05

建立时间是什么意思?精确测量ADC驱动电路建立时间

2021-04-14 06:29:09

请教各位专家: 使用AD9364的FDD模式,将DATA_CLK送入FPGA的时钟输入引脚,用FPGA内部PLL进行倍频。 当AD9364处于ALERT状态时,FPGA内部PLL能够保持锁定状态

2018-08-20 07:20:29

输出? 问题2:回读ox22c=0xe6,显示PLL1未锁定,各位原来9524的PLL1没锁定的,最后都是怎样锁定的?

2018-09-28 15:00:08

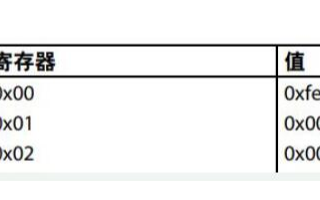

Vcm = 0.4V,REFCLK=120MHz,幅度680mV,8倍内插,PLL时钟2不能锁定,N1为4,N2为4,可能会是哪里的问题?reg08写成自动模式,读出数据为000000,始终不能锁定,会是哪里的问题?

2024-01-26 07:50:02

Select'设置为6'b111111来启动自动搜索功能;但内部PLL无法锁定,再查询0x08寄存器高6bit,显示值又回到了6'b000000。

我手动将

2024-01-15 07:00:26

Vp电压=+5V,当ADF4001未锁定时,CP输出是什么,此时A点的电压是多少?附件PLL无源滤波.bmp745.9 KB

2018-12-11 09:22:21

[/td][td]本人最近调试ADF4350,发现锁定时间达不到要求,但是看数据手册中的例子,发现理论上应该可以达到我的要求,(If a PLL has reference frequencies

2018-11-28 09:09:00

可以自己调整过来,并重新锁定时钟,获得正确的时钟输出;但是,若PLL的输入时钟频率较之原来设定的时钟频率变化较大时(比如,PLL输入时钟频率由50MHz变为200MHz),PLL将无法重新锁定时钟,其输出时钟频率将变为不确定的值。[hide][/hide]

2009-12-22 11:27:13

DN7-DC精确滤波器简化了PLL设计

2019-06-26 15:57:03

我一直在研究E4436B ESG-DP,它在冷却时工作正常,但一旦温度升高,就会在整个GHz频率(1 GHz,2 GHz和3 GHz)失去PLL锁定。 PLL解锁范围仅比整个GHz频率低几MHz,即

2019-03-22 10:23:18

(1.28Gbps))。所以我有6个PLL。我的GTP设计是完全对称的。只有一个MGT_USRCLK模块的PLL(PLL0)被锁定,另一个(PLL1)被锁定一小段时间,然后再被锁定一小段时间再重新锁定一小段时间等等

2019-06-19 11:27:42

定时器详解时钟源计数器定时器周期计算定时器初始化结构体详解程序设置定时器(Timer)最基本的功能就是定时了,比如定时发送 USART 数据、定时采集 AD数据等等。如果把定时器与 GPIO

2021-08-18 06:17:04

操作系统下,由于共享资源的存在,所以在程序的某些地方就会关闭中断,这就使得精确的定时成了一个问题。这样,在CUOSII下,AD采样,定时器,这些要精确定时的任务的执行成了问题。这个问题有什么好的方法可以解决吗?

2019-06-04 03:31:12

你好,我一直在用户电路板设计上使用ST25RU3993,但尚未成功锁定PLL。我试图手动和使用auto命令设置VCO范围。我尝试了各种载波频率/基频/参考频率设置的组合。在尝试解决问题时,我注意到

2019-08-12 10:09:46

6个数码管,利用两个573锁存器,控制片选,段选,利用定时器精确定时1s,显示当前时间attach://201704.rar

2014-06-29 11:13:14

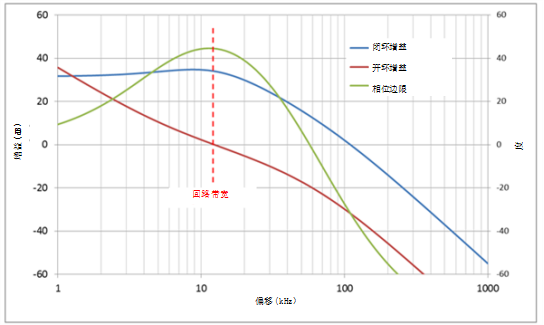

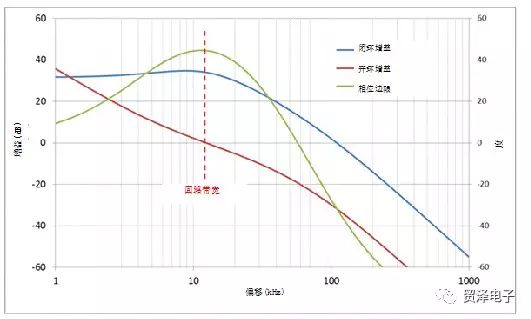

于相位噪声、锁定时间或杂散却并非如此。表1给出了环路带宽对这些性能指标的影响的大致参考。 性能指标最优带宽备注抖动BWJIT最优值一般为BWJIT。在低集成限制更高的一些情况下,有时较窄的环路带宽实际上效果更好。锁定时间无限VCO锁定时间随着环路带宽的增加而提高,但有时会受到VCO校准时间…

2022-11-16 07:56:45

eHi亲爱的社区希望你们中的一些人还在身边。有谁知道我在哪里可以找到有关Virtex-6GTX CDR PLL锁定时间的信息?我试图在一段时间内使用GTX暂停模式,这样它只在需要时突发数据包。因此

2019-11-06 06:23:58

如何测量PLL的频率呢

2024-02-19 07:26:23

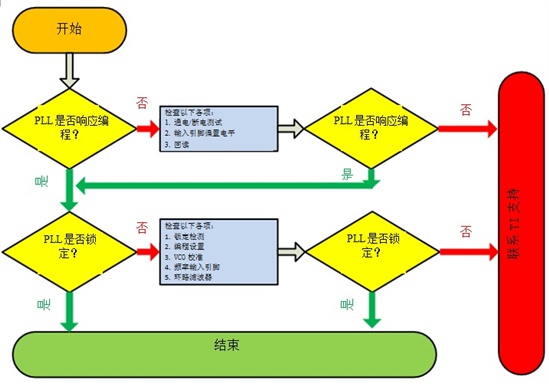

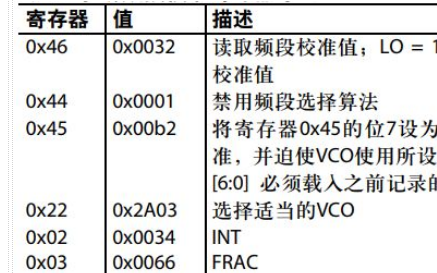

如何手动缩短PLL锁定时间?你知道吗?利用手动频段选择,锁定时间可从典型值4.5 ms 缩短到典型值360 μs。本文以高度集成的解调器和频率合成器ADRF6820 为例,告诉大家如何手动选择频段以缩短PLL锁定时间。

2019-07-31 07:54:28

利用手动频段选择,锁定时间可从典型值4.5 ms 缩短到典型值360 μs。本文以高度集成的解调器和频率合成器ADRF6820 为例,告诉大家如何手动选择频段以缩短PLL锁定时间。First,PLL

2018-08-04 15:00:17

假设您已经通过迭代信息传递相位边限和回路带宽在锁相环(PLL)上花费了一些时间。但遗憾地是,还是无法在相位噪声、杂散和锁定时间之间达成良好的平衡。感到泄气?想要放弃?等一下!你是否试过伽马优化参数?

2019-07-31 07:26:15

。 环路带宽直接决定了锁定时间。环路带宽越大,锁定时间越短,反之,锁定时间越长。频率跳变的大小也决定了锁定时间。频率跳变越大,锁定时间越长,反之,锁定时间越短[11]。窄环路能提高PLL的杂散抑制,提高

2020-12-03 16:06:44

亲爱的大家,是否有人可以提供GTX火箭I / O锁定时间的参考编号?谢谢罗伯托

2020-06-08 11:57:50

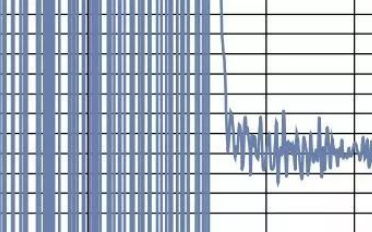

输出频率的子带。该过程需要切换时间,在此期间开环输出频率可以处于各种不同的频率。该频段选择切换时间也被添加到PLL锁定时间,PLL锁定时间本身是PLL环路滤波器带宽的函数。ADF4350在VCO之后

2018-10-26 11:48:38

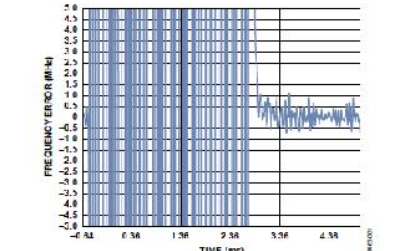

本文将重点介绍瞬态分析功能在脉冲、跳频及PLL频率锁定时间测试中的应用。

2021-06-17 10:37:30

最近单位有一个项目,打算使用AD9364,通信方式采用MF-TDMA,因此对AD9364的锁定时间比较关心,查看了资料,发现AD9364资料中的锁相环锁定时间没有提供,请问有知道AD9364的锁定时间具体是多少么。我们要求锁定时间最大不能超过200us,不知道AD9364能不能满足要求呢,谢谢

2018-10-10 11:22:55

使用ADF4351设计了一个频率源,频率范围1200M-2500M,步进1M,要求跳频时间控制在50us内,通过实际测试只能到100us。现在想知道ADF4351最快的频率锁定时间是多少啊?如果可以达到的话,应如何设置寄存器?参考频率100M,鉴相频率25M,环路带宽为250K。

2018-10-11 09:21:28

ADF9010使用内部VCO,PLL无法锁定的问题。设计中参考时钟为10MHz,要求输出频率为920MHz,R设置为50,P 设置为16/17,B设置为1150,A设置为0,配置完成后,MUXOUT输出R值为1.2kHz,更改R值,输出频率不变,请问配置上有什么特殊考虑?原理图见附件。

2018-07-27 08:09:42

大家好,目前客户评估HMC830做快速跳频源,目前评估的是HMC830的锁定时间能否达到10uS。想咨询一下HMC830的锁定时间能够达到10uS以内呢?我们手头有HMC830的评估板,如何设置HMC830才能做到快速锁频呢?谢谢

2018-09-27 14:12:46

请问stm32如何利用通用定时器实现函数运行时间精确测量?

2021-12-01 07:58:51

从ADF5355的芯片资料上看,其锁定时间很长,超过2.75ms。不知道资料有没有问题?请问各位用过该芯片的大佬,其实际频率锁定时间是否需要这么长?是否有办法加快其锁定?谢谢!

2018-09-27 11:15:02

VCO锁定于正确的频率。锁定速度取决于非线性周跳行为。PLL总锁定时间包括两个部分:VCO频段校准时间和PLL周跳时间。VCO频段校准时间仅取决于PFD频率;PFD频率越高,锁定时间越短。PLL周跳时间由

2018-10-31 10:16:46

[/td][td]本人最近调试ADF4350,发现锁定时间达不到要求,但是看数据手册中的例子,发现理论上应该可以达到我的要求,(If a PLL has reference frequencies

2023-11-27 07:20:06

作为最重要的设计参数之一,选择环路带宽涉及到抖动、相位噪声、锁定时间或杂散之间的平衡。适合抖动的最优环路带宽BWJIT也是数据转换器时钟等许多时钟应用的最佳选择。如果BWJIT并非最佳选择,首先要

2018-08-29 16:02:55

手动选择频段以缩短 PLL 锁定时间——ADRF6820

2021-01-21 06:24:47

本文对电荷泵型锁相环(CPPLL)结构里传统的固定电荷泵电流模式进行了改进,有效减少了锁相环系统的锁定时间。本文提出的PLL设计,在0.6μm标准CMOS工艺、3.3V工作电压下,使用应用

2010-08-03 16:10:33 21

21 对2.5GHz PLL锁定检测电路进行一定层次的正向设计,在此

2010-10-29 17:07:27 0

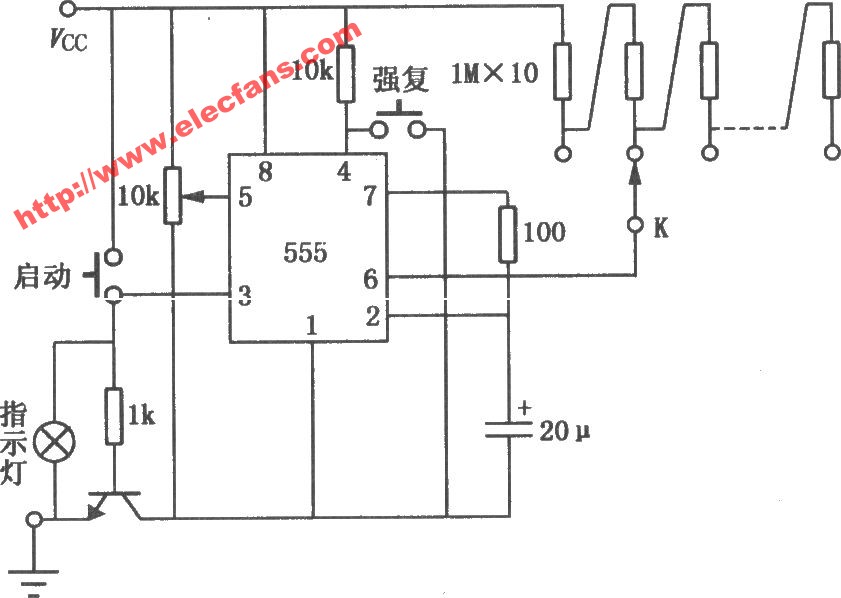

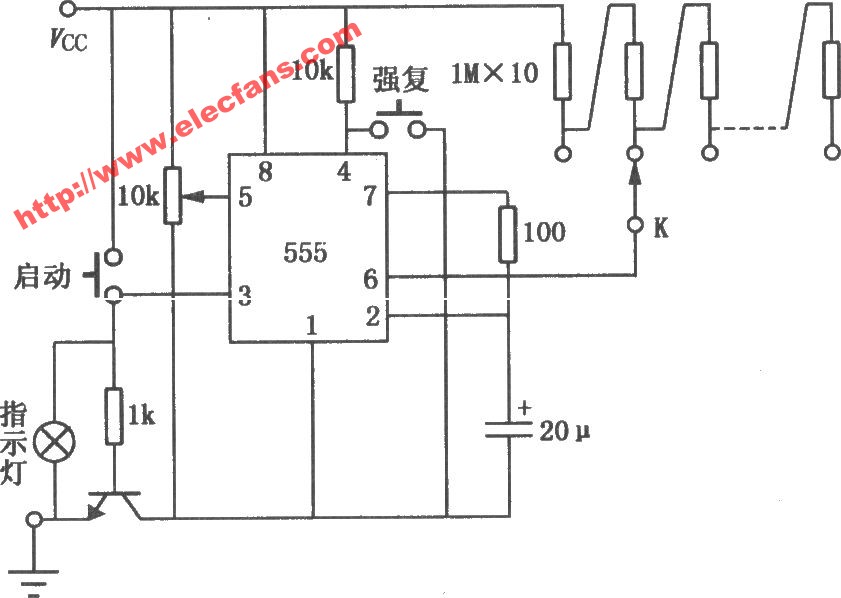

0 电锁定时自停报信电路图:此电路的定时可接电镀工艺要求进行调节,预置时间到,便自动停机,并发出报警卫音响,以便安排工作。

2007-12-14 08:08:30 472

472

555精确定时电路,由时基芯片

2008-10-24 08:51:31 862

862

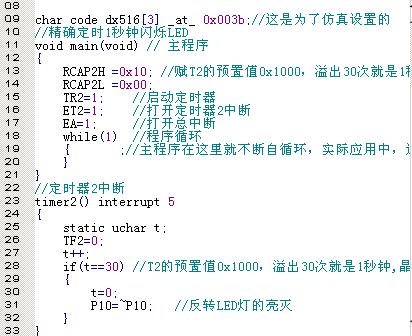

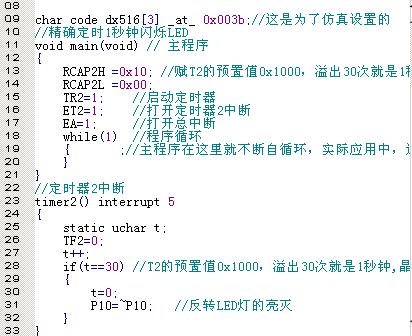

精确定时1秒钟闪灯

这一课,我们将学习如何精确定时1秒钟闪灯。上节介绍过,要精确定时,必须使用自装载方式。这里我们

2009-08-09 23:18:41 1876

1876

关于IGBT导通延迟时间的精确测量方法

0 引 言

绝缘栅双极型晶体管(IGBT)是GTR和MOSFET的一种新型复合器件,自问世以来就以输入阻抗高,开关速度快,通态

2009-11-23 10:33:41 1865

1865

本内容详细介绍了三阶电荷泵锁相环锁定时间的研究,欢迎大家下载学习

2011-09-16 16:37:49 21

21 ADF4xxx系列PLL频率合成器的锁定检测

2011-11-29 15:37:17 38

38 具有高动态性能和锁相精确度的改进PLL设计_薛畅

2017-01-07 15:26:08 20

20 假设您已经通过迭代信息传递相位边限和回路带宽在锁相环(PLL)上花费了一些时间。但遗憾地是,还是无法在相位噪声、杂散和锁定时间之间达成良好的平衡。感到泄气?想要放弃?等一下!你是否试过伽马优化参数?

2017-03-06 17:59:26 3142

3142

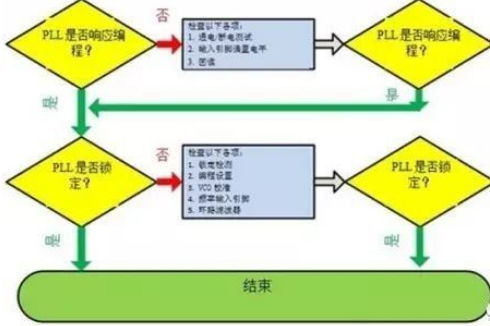

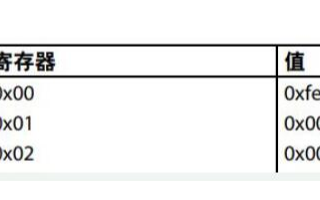

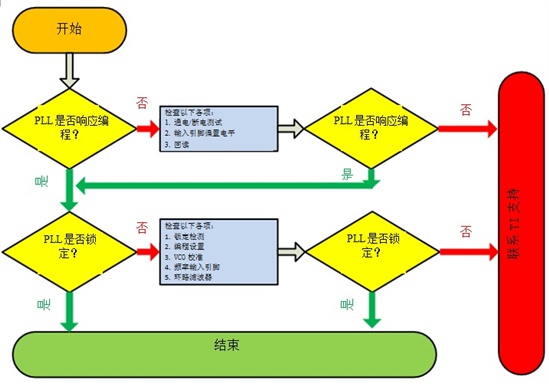

在尝试将锁相环(PLL)锁定时,你是否碰到过麻烦?草率的判断会延长调试过程,调试过程变得更加单调乏味。根据以下验证通行与建立锁定的程序,调试过程可以变得非常简单。第 1 步:验证通信 第一步是验证PLL响应编程的能力。如果PLL没有锁定,无法读回,则尝试发送需要最小量硬件命令工作的软件命令。

2017-04-08 01:56:13 881

881

在尝试将锁相环(PLL)锁定时,你是否碰到过麻烦?草率的判断会延长调试过程,调试过程变得更加单调乏味。根据以

2017-10-16 11:49:30 5147

5147

本文为大家介绍只刷新一次和根据间隔时间一直刷新的定时刷新程序详解。

2018-01-26 16:09:17 6636

6636 PLL锁定有那些检测方法,它们特点是什么?一种是最为简单的数字检测,它利用输入参考的分频信号与VCO反馈的分频信号,在PFD里鉴相的结果,通过连续结果时钟周期检测到鉴相的脉宽小于某值,作为锁定的有效判决规则。这种检测方式,判决方式简单,判断的结果只有锁定和非锁定两种情况。

2018-03-14 16:37:00 4972

4972

在实际的项目开发过程中,常常遇到需要得到一段代码的运行时间,通常的方法是用示波器来测量,这篇博文将用 SysTick 来实现 精确测量 程序运行 的时间。 STM32F4 的内核定时器SysTick是一个24位的定时器,需要注意最大的测量时间。

2018-05-09 14:07:00 5569

5569

校准完成后,PLL的反馈操作使VCO锁定于正确的频率。锁定速度取决于非线性周跳行为。PLL总锁定时间包括两个部分:VCO频段校准时间和PLL周跳时间。VCO频段校准时间仅取决于PFD频率;PFD频率越高,锁定时间越短。

2018-05-11 15:14:34 10847

10847

介绍的是一个简单的模型,可用于精确预测由于PLL系统中的电荷泵和/或运算放大器泄漏电流引起的参考杂散电平。知道如何预测这些电平有助于在PLL系统设计的早期阶段明智地选择环路参数。

2019-04-16 09:03:00 2953

2953

但较高的伽马值也有其蔽处:锁定时间更长。图4所示为不同伽马值下200MHz频率跃变的锁定时间;回路带宽和相位边限保持不变。当伽马值和回路带宽分别为1和3.7,稳定容差在±100Hz范围内,模拟锁定时间值分别为46.5µs与118µs。

2019-08-22 09:03:53 2169

2169

哈希锁定模式是指用户在规定的时间段对于哈希值的原值进行猜测来支付的一种机制。简单讲,就是在智能合约的基础上,双方先锁定资产,如果都在有限的时间内输入正确哈希值的原值,即可完成交易。

2019-09-10 10:56:55 3917

3917 MCS-51单片机的中断响应延迟时间,取决于其它中断服务程序是否在进行,或取决于正在执行的是什么样的指令。单中断系统中的中断响应时间为3~8个 机器周期[1]。无论是哪一种原因引起的误差,在精确定时

2020-01-26 09:04:00 3691

3691

你知道吗?利用手动频段选择,锁定时间可从典型值4.5 ms 缩短到典型值360 µs。本文以高度集成的解调器和频率合成器ADRF6820 为例,告诉大家如何手动选择频段以缩短PLL锁定时间

2020-10-16 10:43:00 0

0 本文以高度集成的解调器和频率合成器 ADRF6820 为例,告诉大家如何手动选择频段以缩短PLL锁定时间。

2020-09-01 11:34:47 3041

3041

AN-873: ADF4xxx系列PLL频率合成器的锁定检测

2021-03-21 09:34:20 6

6 蓝牙时控开关功能新升级,定时时间可精确到秒(已购买用户不用做任何升级,小程序自动更新升级)。 时控开关 小程序使用方法与之前没有变化,在选择定时时间的时候,若有精确到秒的需求,记得选择“秒”即可

2021-09-24 11:54:51 1470

1470 在尝试将锁相环(PLL)锁定时,你是否碰到过麻烦?草率的判断会延长调试过程,调试过程变得更加单调乏味。根据以下验证通行与建立锁定的程序,调试过程可以变得非常简单。

第1步:验证通信

第一步是验证

2021-11-26 16:32:38 5144

5144

作为最重要的设计参数之一,选择环路带宽涉及到抖动、相位噪声、锁定时间或杂散之间的平衡。适合抖动的最优环路带宽BWJIT也是数据转换器时钟等许多时钟应用的最佳选择。如果BWJIT并非最佳选择,首先要

2022-01-11 16:00:28 2150

2150 ADRF6820是一款高度集成的解调器和频率合成器,非常适合用于高级通信系统。 它内置一个宽带I/Q解调器、一个小数N/整数N分频锁相环(PLL)以及一个低相位噪声多核压控振荡器(VCO)。

2022-08-09 11:23:17 968

968

发现抖动、相位噪声、锁定时间或杂散问题?请检查锁相环的环路滤波器带宽

2022-11-02 08:16:24 15

15 定时决定一切:如何使用部分 PLL 创建调制波形

2022-11-04 09:52:13 0

0 作为最重要的设计参数之一,选择环路带宽涉及到抖动、相位噪声、锁定时间或杂散之间的平衡。适合抖动的最优环路带宽BWJIT也是数据转换器时钟等许多时钟应用的最佳选择。如果BWJIT并非最佳选择,首先要做的仍是寻找最优环路带宽。

2023-04-12 10:32:17 1947

1947

pll锁定时间按照频率精度多少来计算 PLL锁定时间是指当PLL尝试将输出频率与输入频率相匹配时所需的时间。这个时间可以用来衡量PLL的性能,因为它决定了PLL能否快速、准确地锁定频率,并且

2023-09-02 15:12:23 811

811 锁相环(PLL)基本原理 当锁相环无法锁定时该怎么处理的呢? 锁相环(Phase Locked Loop, PLL)是一种电路系统,它可以将输入信号的相位锁定到参考信号的相位。在锁相环中,反馈回路

2023-10-23 10:10:15 1353

1353 频率的比例决定了锁定的频率倍数,因此对于VCO的频率稳定性要求比较高。 2. 延迟:VCO的输出延迟对于PLL系统的工作非常重要。如果VCO的输出延迟太大,则可能会导致锁定时间变长或者无法锁定。 3. 噪声:VCO的输出噪声会影响PLL系统的性能和稳定性。因此,要求VCO的输出噪声较

2023-10-30 10:46:44 358

358 锁相环锁定时间取决于哪些因素?如何加速锁定? 锁相环(PLL)是一种常见的电路,用于稳定频率。PLL中的关键是相锁。相锁发挥着将输入频率与参考频率调整到相等的重要作用。在锁相环设计中,锁定时间

2023-10-30 10:51:18 899

899 到芯片逻辑的正确运行。在测试PLL IP时,通常会有多个测试项目,如频率测试、相位噪声、锁定时间、稳定性、误差和漂移等。 但在SoC的ATE测试中,CP阶段通常只进行PLL频率和锁定测试。 那么DFT

2023-10-30 11:44:17 662

662

电子发烧友App

电子发烧友App

评论