Cadence宣布业内首个DDR4 Design IP解决方案在28纳米级芯片上得到验证

2012-09-10 09:53:24 1403

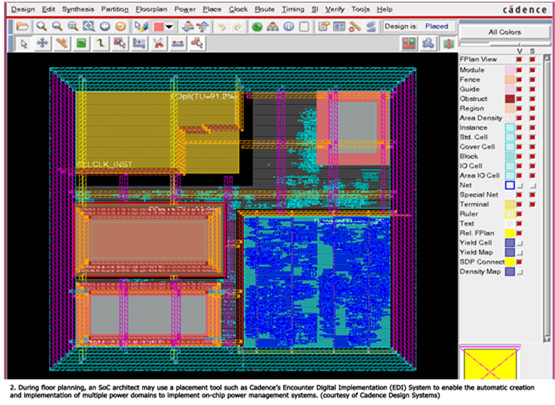

1403 Cadence系统芯片开发工具已经通过台积电(TSMC) 16纳米 FinFET制程的设计参考手册第0.1版与 SPICE 模型工具认证,客户现在可以享用Cadence益华电脑流程为先进制程所提供的速度、功耗与面积优势。

2013-06-06 09:26:45 1236

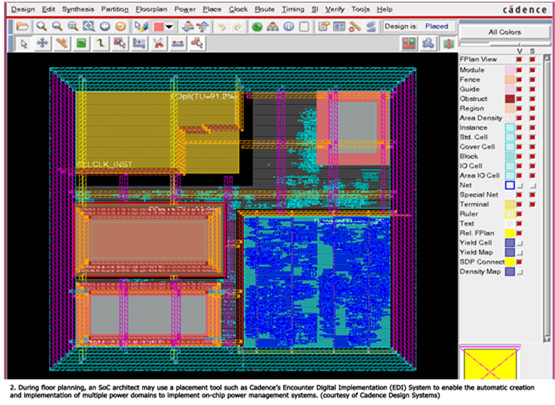

1236 全球电子设计创新领先企业Cadence设计系统公司(NASDAQ: CDNS)今天宣布,全球领先的晶圆厂之一中国中芯国际[0.40 2.56%]集成电路制造有限公司(SMIC)推出一款采用Cadence Encounter数字技术和SMIC

2012-04-11 09:44:30 825

825 么?刚开学,本人想提升电路设计方面的能力,现在电路图很多都看不懂,看懂了又不知其实际应用,求大神给我些学习者方面的书,同学说从电源入手,实践过程中才能了解这些,求大神解惑?

2014-09-02 10:11:31

级设计领域的设计团队提供新技术和增强以提升易用性、生产率和协作能力,从而为PCB设计工程师树立了全新典范。 工程团队在设计和管理当今复杂的电子设计全系统互连时,面临前所未有的挑战。随着PCB平均面积

2018-11-23 17:02:55

Cadence仿真流程Cadence仿真流程[/hide][此贴子已经被作者于2009-8-16 13:47:51编辑过]

2009-08-16 13:47:03

:“我们选择Cadence作为我们RFSiP技术的合作伙伴,因为Cadence有相应的技术和能力,能够和我们共同制定一套在FREESCALE能被广泛采用的解决方案,从而显著提升我们的RFSiP技术

2008-06-27 10:24:12

,“我们为客户开发并提供创新的能力,显见我们对PCB市场的承诺。” 下一代PCB设计流程 最新发布的Cadence Allegro平台,推出了层次布线规划,和全局布线等新技术,大大提升了基于规则驱动

2018-08-28 15:28:45

最新发布的Cadence Allegro平台,推出了层次布线规划,和全局布线等新技术,大大提升了基于规则驱动的先进设计能力。该平台还通过新的使用模式和增强的易用性提供了更好的可用性

2008-06-19 09:36:24

数字芯片设计流程:功能验证之前与工艺库没多大联系,验证芯片设计的功能是否正确,针对抽象的代码进行功能验证理想值。一致性验证确保生成的网表和代码设计功能一致;DFT之后是数字后端。静态时序分析,从逻辑

2021-11-10 06:14:28

方法得到的。一种是用virtuoso等版图编辑工具手工绘制。这在模拟设计中较为普遍。另一种是用Cadence的SE等自动布局布线工具(APR)由网表文件自动产生。芯片失效分析实验室介绍,能够依据国际、国内

2020-02-12 16:09:48

提到纳米技术,人们可能会觉得离自己好远。其实纳米材料在几个世纪前,就已经在陶瓷釉和有色窗玻璃染色剂中使用。1990年代末以来,纳米技术越来越多的投入到应用中。现在,全球各地的科学家和工程师都在对这个

2021-08-31 08:13:56

、东南亚产品,衣鞋等。注意:1.网上很多自己喷上去的,还很好卖,这些附着力很差的,可以说是一次性的,上面有灰尘、水分。鞋子有纳米防水镀膜始需要可靠性测试的。某国际品牌已经在做测试2.街头的那个纳米防水技术,还现场演示。实践是检验真理的唯一标准。忽悠老板姓。

2018-10-09 09:54:28

`7纳米芯片一直被视为芯片业“皇冠上的珍珠”,令全球芯片企业趋之若鹜。在大家热火朝天地竞相布局7纳米工艺时,全球第二大的芯片大厂GlobalFoundries(格罗方德,格芯,以下简称GF)突然宣布

2018-09-05 14:38:53

Marketplace内部,用户可以访问网络商店,在那里可以发现并下载来自Cadence及其渠道合作伙伴的程序,通过最新的、改进的功能与特性强化对其设计工艺与流程的控制。 “Cadence是首家将PCB设计生态体系

2020-07-06 17:49:34

共模滤波电路,电容和电感上的引线要尽量加宽。3、电源的去耦钽电容,应靠近电压调整模块的输出位置,电源电路中的滤波钽电容电压应采用 1/3 降额设计。注:1、变压器的原边和副边:被供电的是原边,输出

2019-02-22 12:03:52

`基于VMware workstation,安装Linux操作系统及相关的EDA软件,配置EDA芯片设计环境,打造个人芯片设计学习平台,练习实践所学芯片设计理论,增强芯片设计能力!加入启芯学堂QQ群:275855756第一讲:第二讲:第三讲:第四讲:第五讲:第六讲:第七讲:`

2013-06-15 11:45:29

开发软件“HqFpga”, 支持布局布线、时序分析、内逻辑分析等任务京微齐力:采用40纳米工艺芯片应用于智能穿戴设备领域,具备100项以上FPGA专利及专有技术(国际专利)授权及二次开发权联捷科技:研发

2021-09-10 14:46:09

结构,相对于半桥结构全桥电路输出功率能力更强,半桥拓扑多用于焊机输出电流315A的焊接电源中。图1 三相输入半桥拓扑图2 三相输入全桥结构2IGBT芯片技术中科君芯IGBT芯片技术历经穿通型(PT

2014-08-13 09:01:33

授权使用正确的低功耗分析和最优化引擎,这些功能要求集成在整个设计流程中。此外,在65纳米芯片设计中,约有50%的设计工作是混合信号设计。传统的模拟设计流程与数字工作处于完全隔离的状态,如何把模拟和数字

2019-05-20 05:00:10

后,智慧屏业务就面临了极大不确定性。中国本土晶圆厂中芯国际拥有量产 28nm 芯片的能力,但是也不可避免的会...

2021-07-23 06:11:51

如何提升CPU芯片处理事件能力?

2022-02-07 09:07:12

目标检测的模型集成方法及实验常见的提升模型能力的方式

2021-02-24 07:10:29

本帖最后由 carey123 于 2014-12-9 15:45 编辑

现在网络上广为流传的电路设计能力判断方法,可大致分为两类:一类偏向于“玄学”,比如--电路设计的九个层次一文,内容

2014-12-09 15:44:18

如何设计才能提升LED的驱动能力?

2021-04-09 06:57:08

首款40纳米TD基带芯片出货量已经超过1000万片。李力游表示,在国内TD领域,展讯的市场份额已经达到约50%,其芯片产品得到了国际一线品牌手机厂商的采纳,比如,三星手机GALAXY S Ⅱ就是采用展

2011-10-27 11:50:07

小的设计,因为前者的工作平台是工作站后者是PC)。全定制数字Asic或者混合信号ASIC(从下到上与从上到下结合)当需要制作全定制的数字芯片时,传统的从上到下的设计流程就不完全奏效了。其中最大的不同就是全定制

2013-01-07 17:10:35

展开深度合作,美国将切断中国企业生产产品所需要的美国设备以及软件的供应。对此,拜登***可能会选取的攻击目标为中国的半导体集团公司中芯国际,其他无视美国制裁禁令继续向俄罗斯供应芯片或者先进技术的中国企业

2022-03-11 10:34:37

产品采用的40nm四核A7芯片相比,RK3358J具有同等频率下综合性能提升40%左右而功耗降低10%的明显优势,长时间工作温升低,具有更高的可靠性。 RK3358J工规芯片,面向集中器、采集器、能源

2022-07-25 15:48:24

几个工艺段,分别安装在几个楼层中,这样各个工艺段的货物如果使用传统的货物电梯进行传送,将会给生产带来许多不便,而且还会影响生产效率。因此,设计一个直接连接不同楼层的生产线的提升机是必要的。1、工艺流程

2011-09-29 09:47:16

EUV主要用于7nm及以下制程的芯片制造,光刻机作为集成电路制造中最关键的设备,对芯片制作工艺有着决定性的影响,被誉为“超精密制造技术皇冠上的明珠”,根据之前中芯国际的公报,目...

2021-07-29 09:36:46

Cadence 仿真流程:第一章 在Allegro 中准备好进行SI 仿真的PCB 板图1)在Cadence 中进行SI 分析可以通过几种方

2008-07-12 08:56:05 0

0 cadence 视频教程 (第40课):cadence SPB 15.7 视频教程,手把手教你学习cadence软件使用方法。本套视频教程是于博士信号完整性研究网于争博士主讲。从一个工程师的角度出发讲解软件的操

2009-09-16 18:45:05 0

0 台积电率先量产40纳米工艺

台积电公司日前表示,40纳米泛用型(40G)及40纳米低耗电(40LP)工艺正式进入量产,成为专业集成电路制造服务领域唯一量产40纳米工艺的公司

2008-11-22 18:27:07 724

724 2009年3月4日,Cadence设计系统公司今天宣布生物指纹安全解决方案领先厂商UPEK®, Inc.已经整合其设计流程,并选择Cadence®作为其全芯片数字、模拟与混合信号设计的

2009-03-05 12:14:18 519

519 Cadence推出首个TLM驱动式设计与验证解决方案提升基于RTL流程的开发效率

Cadence设计系统公司推出首个TLM驱动式协同设计与验证解决方案和方法学,使SoC设计师们可以尽

2009-08-11 09:12:18 499

499 中芯国际将45纳米工艺技术延伸至40纳米以及55纳米

上海2009年10月14日电 -- 中芯国际集成电路制造有限公司(“中芯国际”,纽约

2009-10-15 08:22:44 793

793 中芯国际采用Cadence DFM解决方案用于65和45纳米 IP/库开发和全芯片生产

Cadence 模型化的 Litho Physical 和 Litho Electrical

2009-10-19 17:48:11 461

461 Cadence 模型化的 Litho Physical 和 Litho Electrical AnalyzerLitho Physical 与 Litho Electrical Analyzer 解决方案提供了快速、精确硅认证的全芯片电气 DFM 验证流程

2009-10-20 09:54:02 990

990 中芯国际(SMIC)和Cadence 共同推出用于65纳米的低功耗解决方案Reference Flow 4.0

完全集成的能效型流程令快速、轻松地设计低功耗尖端器件成为可能

2009-10-31 07:48:01 1228

1228 中芯国际(SMIC)和Cadence共同推出用于65纳米的低功耗解决方案Reference Flow 4.0

全球电子设计创新领先企业Cadence设计系统公司今天宣布推出一款全面的低功耗设计流程,面向

2009-11-04 17:05:17 589

589 芯邦采用Cadence Incisive Xtreme III系统提升SoC验证实效

全球电子设计创新领先企业Cadence设计系统公司今天宣布,位于中国深圳的、无晶圆厂集成电路设计领先企业芯邦科

2010-03-02 10:32:47 573

573 中芯国际力争在2010年实现45纳米小批量试产

2010年,中芯国际将加强65纳米的嵌入式工艺平台和32纳米关键模块的研发;同时力争实现45纳米和40纳米技术的小批量试产

2010-03-08 09:33:16 471

471 三星电子推出40纳米级动态存储芯片

据韩国《中央日报》报道,世界著名存储芯片企业三星电子在全球率先推出40纳米级32GB DRAM(动态随机存取记

2010-04-07 12:36:05 713

713 新思科技完整实施流程助力英飞凌在中国成功实现首款40纳米3G基带处理器芯片设计和一次流片成功

中国北京和西安,2010年8月9日—全

2010-08-11 14:39:39 510

510 Cadence设计系统公司日前宣布展讯通信有限公司实现了其首款40纳米低功耗GSM/GPRS/EDGE/TD-SCDMA/HSPA商用无线通信芯片的一次性流片成功。

2011-01-22 10:04:17 988

988 即将上市的这种新流程支持Cadence的硅实现方法,专注于独一无二且普遍深入的设计意图、提取与从RTL到GDSII,然后到封装。硅实现是EDA360构想的一个关键组成部分。

2011-06-28 09:44:23 455

455 三星电子有限公司使用Cadence统一数字流程,从RTL到GDSII,成功实现了20纳米测试芯片的流片

2011-07-27 08:47:49 967

967 展讯董事长兼CEO李力游在接受搜狐IT专访时透露,展讯将于今年年底前推出基于40纳米技术的LTE芯片

2011-08-17 08:39:12 686

686 全球电子设计创新领先企业Cadence设计系统公司(NASDAQ: CDNS),宣布Giantec Semiconductor Corp.已采用Cadence® Virtuoso®统一定制/模拟(IC6.1)以及Encounter®统一数字流程生产其混合信号芯片。

2011-09-27 11:06:26 1483

1483 近日,创毅正式推出兼容3GPP R9版本的40nm工艺 WarpDrive 5000芯片。该款芯片支持TD-LTE FDD/TDD共模,采用40纳米工艺,兼容3GPP LTE 标准 (Release-9)

2011-09-30 09:38:42 872

872 灿芯半导体与中芯国际及ARM今日联合宣布,采用中芯国际40纳米低漏电工艺的 ARM Cortex-A9 MPCore 双核测试芯片首次成功流片。

2012-02-28 09:06:12 1148

1148 全球电子设计创新领先企业Cadence设计系统公司日前宣布推出最新版Cadence Encounter RTL-to-GDSII流程.

2012-03-10 09:44:06 763

763 北京时间4月26日消息,据国外媒体报道,展讯通信今日宣布,业界首款基于40纳米CMOS工艺的2.5G基带芯片产品SC6530已经实现商业化应用。

2012-04-27 14:05:16 854

854 据美国科技博客AnandTech报道,苹果已经开始出售升级版iPad 2,通过32纳米A5处理器将电池续航能力提升了16%。

2012-05-04 18:02:37 962

962 Cadence 设计系统公司日前宣布,汽车零部件生产商Denso公司在改用了Cadence定制/模拟与数字流程之后,在低功耗混合信号IC设计方面实现了质量与效率的大幅提升。将Cadence Encounter RTL-to-G

2012-09-04 09:31:59 811

811 全球电子设计创新领先企业Cadence设计系统公司日前宣布TSMC已选择Cadence解决方案作为其20纳米的设计架构。Cadence解决方案包括Virtuoso定制/模拟以及Encounter RTL-to-Signoff平台。

2012-10-22 16:48:03 909

909 该14纳米产品体系与芯片是ARM、Cadence与IBM之间在14纳米及以上高级工艺节点上开发系统级芯片(SoC)多年努力的重要里程碑。使用FinFET技术以14纳米标准设计的SoC能够大幅降低功耗。 这

2012-11-16 14:35:55 1270

1270 Cadence设计系统公司日前宣布Avago Technologies在大型28纳米网络芯片设计中使用其EDI系统,大幅度加快设计进度,提高了工程效率。Avago实现1GHz的性能,比之前所用软件设计的芯片提高57%。

2013-02-04 09:17:00 1150

1150

全球电子设计创新领先企业Cadence设计系统公司(NASDAQ:CDNS)近日宣布,GLOBALFOUNDRIES已携手Cadence®,为其20和14纳米制程提供模式分类数据

2013-05-13 10:20:02 768

768 光刻物理分析器成功完成20纳米系统级芯片(SoC)测试芯片流片。双方工程师通过紧密合作,运用Cadence解决方案克服实施和可制造性设计(DFM)验证挑战,并最终完成设计。

2013-07-09 15:53:24 769

769 全球电子创新设计Cadence公司与上海华力微电子,15日共同宣布了华力微电子基于Cadence Encounter数字技术交付55纳米平台的参考设计流程。华力微电子首次在其已建立55纳米工艺上实现了从RTL到GDSII的完整流程。

2013-08-16 11:08:11 1382

1382 全球电子设计创新领先企业Cadence设计系统公司(NASDAQ:CDNS)与上海华力微电子有限公司,今天共同宣布华力微电子基于Cadence ® Encounter® 数字技术交付出55纳米平台的参考设计流程。

2013-08-16 12:02:40 1445

1445 ® 数字工具流程,应用于其新款SMIC Reference Flow 5.1,一款为低功耗设计的完整的RTL-GDSII 数字流程。Cadence流程结合了先进功能,以帮助客户为40纳米芯片设计提高功率、性能和面积。

2013-09-05 16:50:41 748

748 ) 通过采用Cadence®完整的工具流程,已成功完成该公司最大型的SoC (系统单芯片) 项目开发,该项目是用于4G基站的3亿门芯片设计。通过在其分层式 (hierarchical) 设计流程中部

2013-11-19 10:30:13 886

886 全球知名电子设计创新领先公司Cadence设计系统公司 (NASDAQ: CDNS),今日宣布台积电采用了Cadence®16纳米FinFET单元库特性分析解决方案。

2014-10-08 19:03:22 1593

1593 详细介绍Cadence的仿真流程

有需要的朋友下来看看

2015-12-08 14:49:11 0

0 2016年3月22日,中国上海——楷登电子(美国 Cadence 公司,NASDAQ: CDNS)今日宣布,用于10纳米 FinFET工艺的数字、定制/模拟和签核工具通过台积电(TSMC)V1.0设计参考手册(DRM)及SPICE认证。

2016-03-22 13:54:54 1026

1026 “我们与 Cadence 密切合作开发参考流程,帮助我们的客户加快其差异化的低功耗、高性能芯片的设计,”中芯国际设计服务中心资深副总裁汤天申博士表示,“Cadence创新的数字实现工具与中芯国际28纳米工艺的紧密结合,能够帮助设计团队将28纳米设计达到更低的功耗以及更快的量产化。”

2016-06-08 16:09:56 2242

2242 赛灵思、Arm、Cadence和台积公司今日宣布计划在 2018 年交付 7 纳米 FinFET 工艺芯片。这一测试芯片旨在从硅芯片层面证明 CCIX 能够支持多核高性能 Arm CPU 和 FPGA 加速器实现一致性互联。

2017-09-25 11:20:20 6826

6826 苹果明年推出的新手机采用的 A12 芯片将是台积电 7 纳米制程生产,报导指出,全球只有 2 家公司真的有能力最快在明年推出7纳米芯片,那就是苹果和三星 (005930-KR)。

2017-12-21 11:47:52 14427

14427 电路设计能力的判断方法 现在网络上广为流传的电路设计能力判断方法,可大致分为两类:一类偏向于“玄学”,比如--电路设计的九个层次一文,内容是玄之又玄,能达到其最高九段标准的,地球上可能找不几个人。

2018-04-14 12:37:00 19225

19225

现在网络上广为流传的电路设计能力判断方法,可大致分为两类:一类偏向于“玄学”,比如--电路设计的九个层次一文,内容是玄之又玄,能达到其最高九段标准的,地球上可能找不几个人。

2018-05-29 17:12:09 4317

4317

中芯国际14纳米芯片的量产,意味着:在今年上半年,我们国产手机就能用上中端性能的国产芯片了!要知道,华为荣耀8XMax、红米note7、vivo X21用的都是14纳米芯片。

2019-02-25 13:54:58 18116

18116 采用极紫外(EUV)光刻技术的Cadence 数字全流程解决方案已通过Samsung Foundry 5nm早期低功耗版(5LPE)工艺认证。

2019-07-11 16:36:47 3435

3435 加入我们来看看你可以减少设计时间与垫使用自动化专业Rigid-Flex设计能力。

2019-10-18 07:02:00 2276

2276 楷登电子(美国 Cadence 公司,NASDAQ:CDNS)今日发布已经过数百次先进工艺节点成功流片验证的新版 Cadence 数字全流程,进一步优化功耗,性能和面积,广泛应用于汽车,移动,网络

2020-03-18 17:01:56 2710

2710

任正非表示:“我们国家要重新认识芯片问题,芯片的设计当前中国已经步入世界领先,华为目前积累了很强的芯片设计能力;芯片的制造中国也是世界第一,在台湾。

2020-11-16 14:42:57 2514

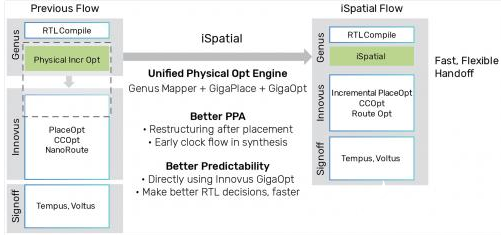

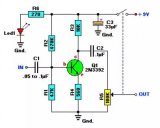

2514 )。 Cadence数字全流程iSpatial技术流程采用了支持机器学习(ML)功能的统一布局布线和物理优化引擎等多项业界首创技术,吞吐量最高提升3倍,PPA最高提升20%,助力实现卓越设计。由于其对用户

2020-11-26 11:04:46 2406

2406 12月23日消息,苹果公司已预定台积电基于3纳米工艺芯片的生产能力,以便在其iOS产品和自研电脑芯片中使用。

2020-12-23 10:17:01 1568

1568 Cadence Safety Solution 包括新的 Midas Safety Platform,为模拟和数字流程提供基于 FMEDA 功能安全设计和验证的统一方案 该安全流程方案为汽车、工业

2021-10-26 14:24:34 4050

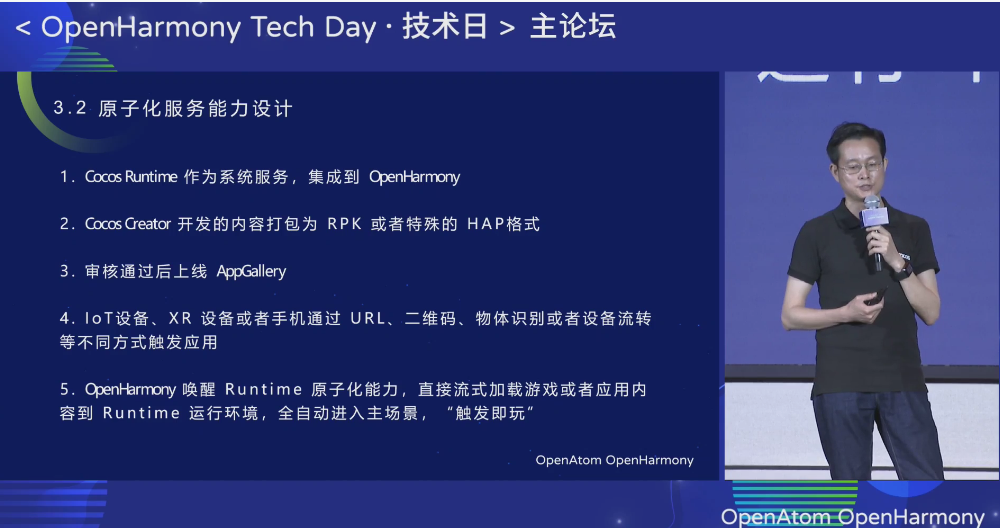

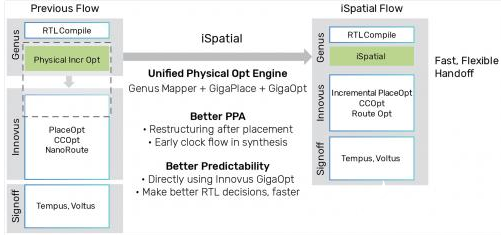

4050 主要讲解了原子化大服务设计能力,其中主要包括五点

2022-04-25 11:02:56 731

731

楷登电子(美国 Cadence 公司,NASDAQ:CDNS)今日宣布,随着新的生产部署完成,客户加速采用 Cadence® Cerebrus™ Intelligent Chip Explorer。

2022-06-14 16:42:30 1825

1825 楷登电子(美国 Cadence 公司,NASDAQ:CDNS)今日宣布,其数字和定制 / 模拟设计流程已获得 TSMC N3E 和 N4P 工艺认证,支持最新的设计规则手册(DRM)。

2022-06-17 17:33:05 4800

4800 中国上海,2022 年 10 月 27 日 —— 楷登电子(美国 Cadence 公司,NASDAQ:CDNS)今日宣布,Cadence 数字和定制/模拟设计流程已获得台积电最新 N4P 和 N3E

2022-10-27 11:01:37 940

940 联华电子(NYSE:UMC;TWSE:2303)与楷登电子(美国 Cadence 公司,NASDAQ:CDNS)今日共同宣布,采用 Integrity 3D-IC 平台的 Cadence 3D-IC 参考工作流程已通过联电的芯片堆栈技术认证,将进一步缩短产品上市时间。

2023-02-03 11:02:23 1417

1417 的先进设计。另一款 CPU 设计采用 AI 赋能的 Cadence Cerebrus Intelligent Chip Explorer 和完整的数字设计流程,借助台积电 N5 制程工艺,成功让功耗降低 8%,设计面积缩小 9%,同时显著提升了工程效率。

2023-02-06 15:02:48 1048

1048 楷登电子(美国 Cadence 公司,NASDAQ:CDNS)近日宣布,Cadence 数字和定制/模拟设计流程已通过 TSMC N3E 和 N2 先进工艺的设计规则手册(DRM)认证。两家公司还发

2023-05-09 10:09:23 708

708 已经过 SF2 和 SF3 流程认证 ● Cadence 数字全流程针对先进节点实现了最佳 PPA 结果 ● Cadence 定制/模拟工具,包括基于 AI 的 Virtuoso Studio

2023-07-05 10:10:01 322

322 已经过 SF2 和 SF3 流程认证 ● Cadence 数字全流程针对先进节点实现了最佳 PPA 结果 ●Cadence 定制/模拟工具,包括基于 AI 的 Virtuoso Studio,已针对

2023-07-05 10:12:14 381

381 的 Cadence 流程,以十足把握交付各类 HPC 及消费电子应用 中国上海,2023 年 7 月 14 日——楷登电子(美国 Cadence 公司,NASDAQ:CDNS)近日宣布其数字和定制/模拟

2023-07-14 12:50:02 381

381

内容提要 Cadence 数字全流程涵盖关键的新技术,包括一款高精度且支持大规模扩展的寄生参数 3D 场求解器 Cadence Cerebrus 由 AI 驱动,支持 N2 制程,可大幅提高客户

2023-10-10 16:05:04 270

270 据了解ACCEL芯片的光学芯片部分只要采用百纳米级别工艺,而电路部分更是可以采用180纳米CMOS工艺就能生产这种芯片,用如此落后的工艺却能将芯片性能提升3000倍,与当前的7纳米工艺芯片性能相当。

2023-11-03 16:29:08 377

377

作为全球领先的芯片封测企业,长电科技深刻理解先进的封装设计能力对于确保半导体行业的产品性能、功能和成本至关重要。大规模高密度的集成电路为产品设计提供了极大的灵活性。例如Chiplet等前沿技术包含

2023-12-18 11:11:46 390

390

电子发烧友App

电子发烧友App

评论