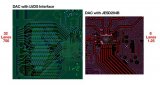

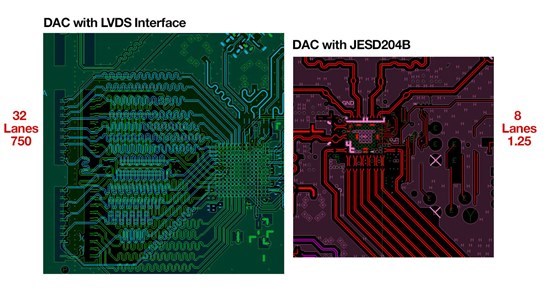

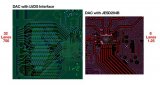

更有优势。采用JESD204的设计拥有更快的接口带来的好处,能与转换器更快的采样速率同步。此外,引脚数的减少导致封装尺寸更小,走线布线数更少,从而极大地简化了电路板设计,降低了整体系统成本。该标准可以方便地调整,从而满足未来需求,这从它已经

2020-11-24 14:41:40 2042

2042

开发串行接口业界标准JESD204A/JESD204B的目的在于解决以高效省钱的方式互连最新宽带数据转换器与其他系统IC的问题。

2021-11-01 11:24:16 5783

5783

大家好,我正在尝试在kintex-7 FPGA中构建一个运行速度为5Gbps的JESD204B ADC和DAC接口。根据产品指南文档,我在vivado 2014.1中生成了发送和接收内核,更新了

2018-10-19 14:37:42

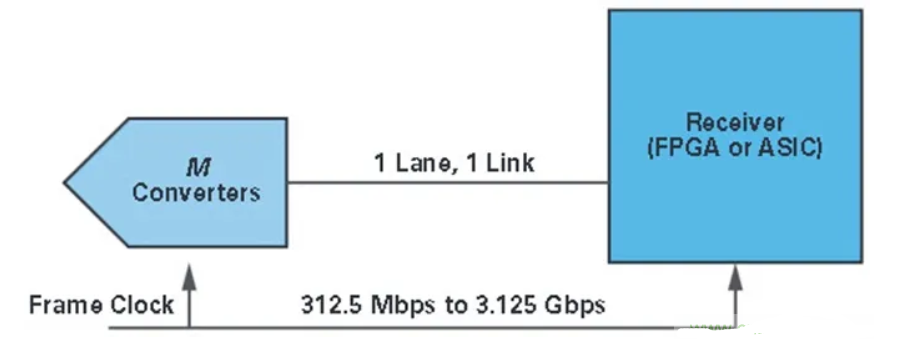

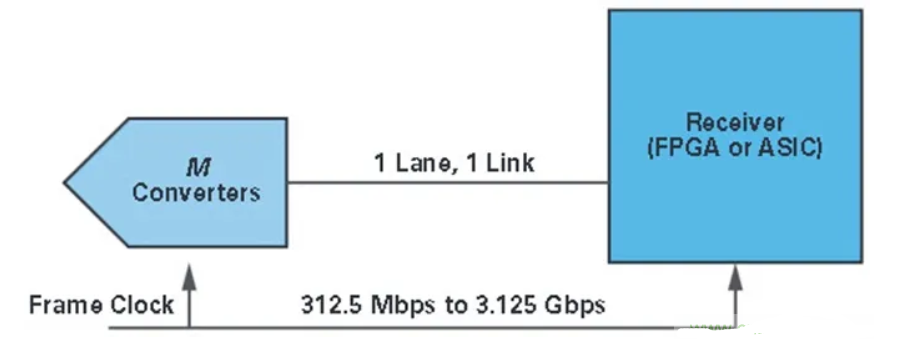

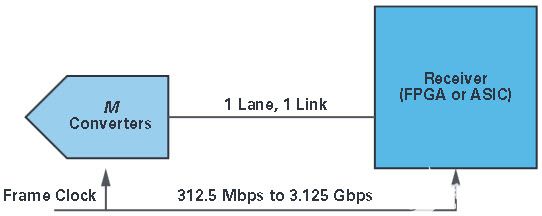

数模转换器(DAC);本文将集中探讨其在模数转换器中的应用。JESD204(2006)2006年4月, JESD204最初版本发布。该版本描述了转换器和接收器(通常是FPGA或ASIC)之间数Gb的串行

2019-05-29 05:00:03

`描述采用均衡技术可以有效地补偿数据转换器的 JESD204B 高速串行接口中的信道损耗。此参考设计采用了 ADC16DX370 双 16 位 370 MSPS 模数转换器 (ADC),该转换器利用

2015-05-11 10:40:44

的时钟规范,以及利用TI 公司的芯片实现其时序要求。1. JESD204B 介绍1.1 JESD204B 规范及其优势 JESD204 是基于SerDes 的串行接口标准,主要用于数模转换器和逻辑器件

2019-06-19 05:00:06

和 CMOS 接口提供的优势。有了 JESD204B,您无需再:使用数据接口时钟(嵌入在比特流中)担心信道偏移(信道对齐可修复该问题)使用大量 I/O(高速串行解串器实现高吞吐量)担心用于同步多种 IC

2018-09-13 14:21:49

in JESD204B high speed serial interfaces for data converters. This reference design features the ADC16DX370, a

2018-08-09 08:40:10

的优势。有了 JESD204B,您无需再:使用数据接口时钟(嵌入在比特流中)担心信道偏移(信道对齐可修复该问题)使用大量 I/O(高速串行解串器实现高吞吐量)担心用于同步多种 IC 的复杂方法(子类…

2022-11-21 07:02:17

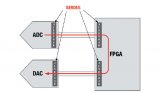

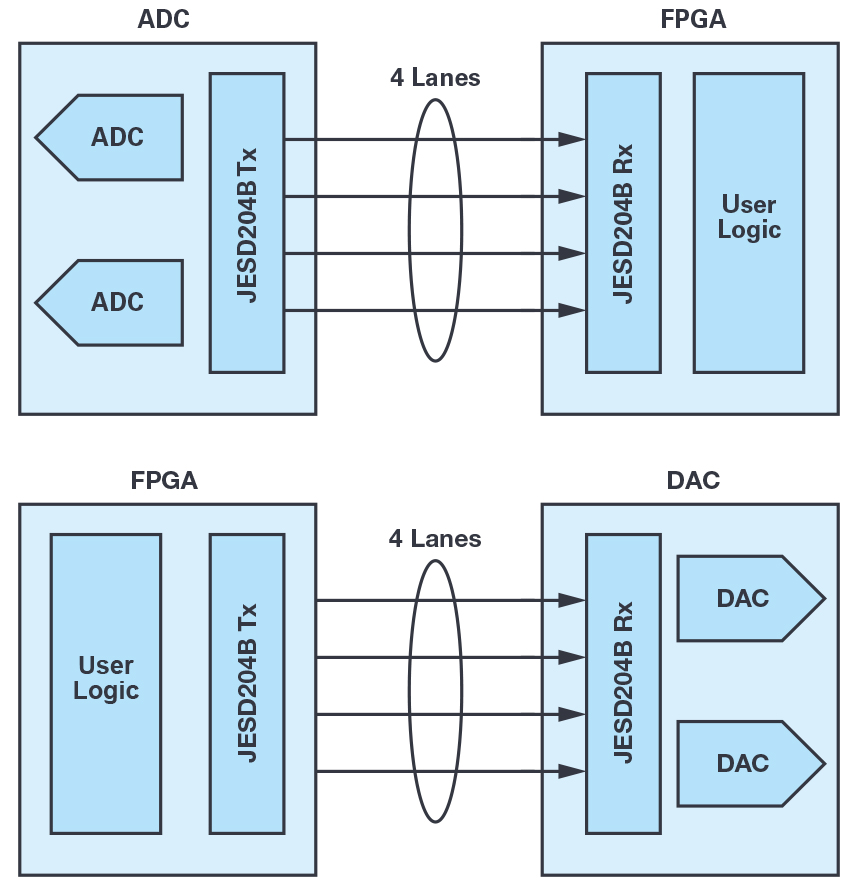

在使用最新模数转换器 (ADC) 和数模转换器 (DAC) 设计系统时,我已知道了很多有关 JESD204B 接口标准的信息,这些器件使用该协议与 FPGA 通信。那么在解决 ADC 至 FPGA

2021-04-06 06:53:56

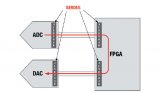

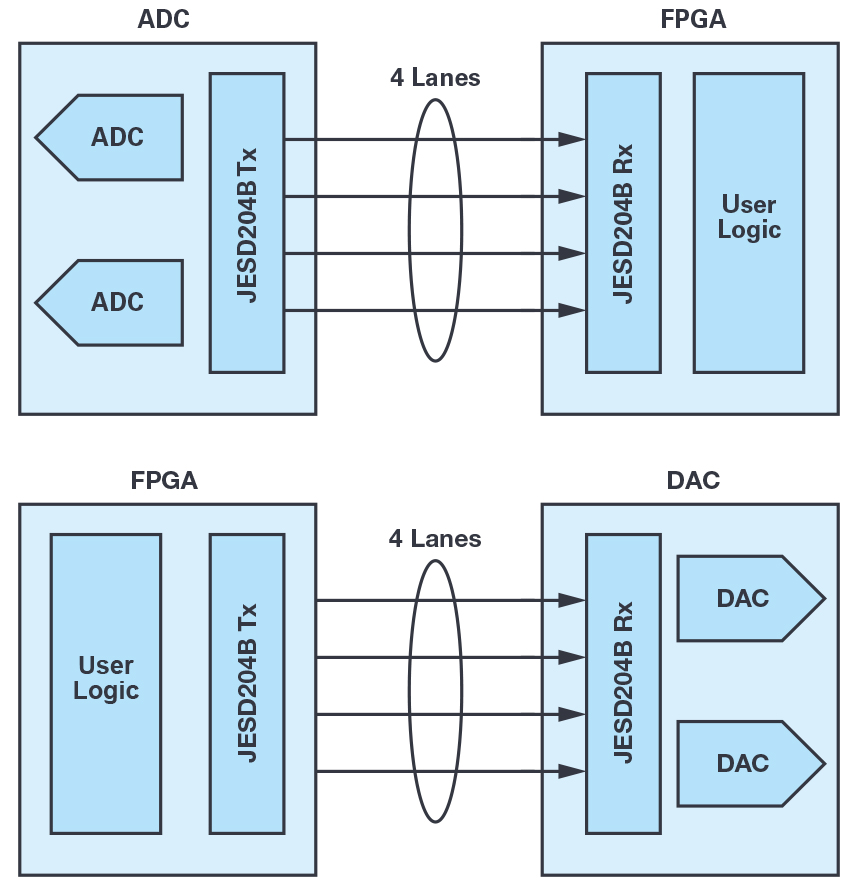

如果您有接触使用 FPGA 的高速数据采集设计,没准听说过新术语“JESD204B”。我在工作中看到过很多工程师询问有关 JESD204B 接口的信息以及它如何同 FPGA 协作。他们特别感兴趣

2022-11-23 06:35:43

的JESD204发布版中。

问:我为转换器分配的JESD204B通道在系统板上无法顺利路由至FPGA。交叉对太多,非常容易受串扰影响。能否重新映射JESD204B的通道分配,改善布局?

答:虽然转换器

2024-01-03 06:35:04

这种应用,您应该考虑 LVDS 接口,因此它没有在 JESD204B 上进行数据串行化的延迟。如欲了解有关 JESD204B 的更得意详情,敬请参考其它资源:深入了解 JESD204B 接口的演变及其

2018-09-18 11:29:29

到解帧器的接收器延迟。来自同一个系统中两个不同ADC的数据可能各自具有独特的确定性延迟。与简单的串行链路配置不同——比如低压差分信号 (LVDS)——JESD204B接口将数据样本打包为定义帧。几个

2018-10-15 10:40:45

在JESD204C入门系列的 第1部分 中,通过描述它解决的一些问题,对JESD204标准的新版本进行了说明。通过描述新的术语和特性来总结B和C版本标准之间的差异,然后逐层概述这些差异。因为第1部分已经奠定了理解基础,现在我们来进一步研究一下JESD204C标准几个更值得注意的新特性。

2020-12-28 06:15:45

的时间内处理更多信息。相应地,对快速增长的高带宽进行测试与分析便意味着需要使用速度更快、容量更大的电子测试设备。 对数据不断增长的需求导致JEDEC固态技术协会需要引入新的 JESD204 标准,以实现

2021-01-01 07:44:26

我们购买了两个评估套件:ZC706和ARDV9371,将它们连接在一起。现在我们要修改从ADI获得的FPGA代码。我已经安装了ZC706的许可证,后来又安装了JESD204的评估许可证(见附件

2019-01-02 14:53:44

有关ADI公司兼容JESD204标准的更多产品。随着转换器速度和分辨率的提高,对于效率更高的数字接口的需求也随之增长。随着JESD204串行数据接口的发明,业界开始意识到了这点。接口规范依然在不断发展中

2019-06-17 05:00:08

嗨,我正在使用ISE14.6和Vivado 2013.2并且我曾要求获得JESD204的评估许可证,当我将许可证映射到VIvado时,我也得到了相同的结果,JESD204 LogicIP核心未突出

2020-03-11 06:05:53

因实际需求,本人想使用JESD204b的ip核接收ADC发送过来的数据,ADC发送的数据链路速率是15gbps, 厂家说属于204b标准。我看到jesd204b的ip核标准最大是12.5gbps,但是支持的支持高达16.375 Gb/s的非标准线速率。请问我可以使用这个IP核接收ADC的数据吗?

2020-08-12 09:36:39

用于高速 ADC 的串行接口

2019-09-06 06:01:13

到的数据流,并将处理后产生的数据流发送出去。串行LVDS与JESD204B的对比在串行LVDS和JESD204B接口间作出选择为了在使用LVDS和多种版本JESD204串行接口规范的转换器产品间做出最佳选择

2019-05-29 05:00:04

具有可重复的确定性延迟。随着转换器的速度和分辨率不断提升,JESD204B接口在ADI高速转换器和集成RF收发器中也变得更为常见。此外,FPGA和ASIC中灵活的串行器/解串器(SERDES)设计正逐步

2018-10-16 06:02:44

目前,我在设计中想使用ZYNQ 7015系列的FPGA,利用JESD204 IP核接收A/D转换器AD9683转换完成后的数据。但是JESD204 IP核的端口很多,我不知道应该如何将AD9683

2023-12-15 07:14:52

传输的ADC不仅在体积、功耗和数据传输速率都比并行总线传输的ADC更具优势。在高速数据采集传输系统中,串行总线传输的ADC已成为今后的发展趋势。在研究了高速串行传输技术后,设计了基于JESD204B协议

2019-12-04 10:11:26

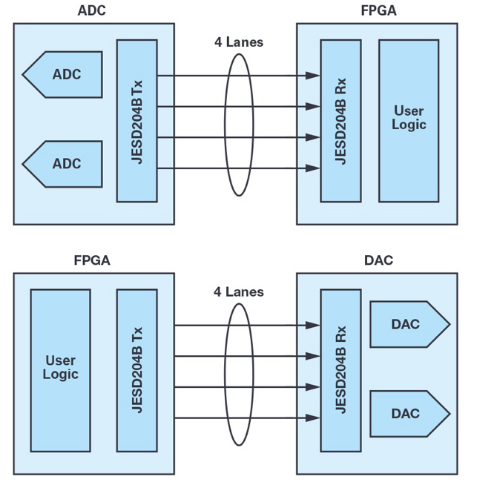

,具有高速并串转换的作用。2、使用JESD204B接口的原因a.不用再使用数据接口时钟(时钟嵌入在比特流中,利用恢复时钟技术CDR)b.不用担心信道偏移(信道对齐可修复此问题,RX端FIFO缓冲器)c.

2019-12-03 17:32:13

嗨,我必须在Kintex 7上导入为Virtex 6开发的代码,以便将JESD204B标准中的ADC输出接口。我修改了代码和ucf文件,以便在演示板MC705上实现它。Synthesize

2020-05-21 14:22:21

R_10002_JEDEC_JESD204A数据转换器接口技术分析

2012-08-14 12:22:22

为什么JESD204内核不使用GTX通道绑定功能来对齐通道?我试图从AD接收数据,AD使用JESD204B协议传输数据。我的计划是使用GTX核心并自己编写JESD部分。我的项目需要两个车道,我在初始

2020-08-18 10:03:51

JESD204是什么?JESD204标准解析,为什么我们要重视它?

2021-04-13 06:14:53

描述JESD204B 链路是数据转换器数字接口的最新趋势。这些链路利用高速串行数字技术提供很大的益处(包括增大的信道密度)。此参考设计解决了其中一个采用新接口的挑战:理解并设计链路延迟。一个示例实现

2018-11-21 16:51:43

JESD204B数模转换器的时钟规范是什么?JESD204B数模转换器有哪些优势?如何去实现JESD204B时钟?

2021-05-18 06:06:10

。 FPGA连通性以及JESD204B和JESD204C 您可能要解决的最大问题之一是如何在FPGA中获取数据。尽管LVDS和CMOS是简易接口,但它们在设备上每个管脚上支持的速度极其有限。随着更新

2021-01-07 17:37:46

和DAC不能通过这些高速串行接口进行配置,就是说FPGA与转换器无法与任何常用标准接口,利用高串行-解串(SERDES)带宽。新型转换器与JESD204B之类的FPGA接口较为复杂,如何让JESD204B在FPGA上工作?FPGA对于JESD204B需要多少速度?

2021-04-06 09:46:23

lanes and channels won’t be able to effectively use LVDS or parallel CMOS. 为了在使用LVDS和多种版本JESD204串行

2021-11-03 07:00:00

JESD204b接口已经在国内好几年,但是几乎没有一篇文章和其实际应用相关。其实对于一个关于JESD204b接口ADC项目来讲一共大致有5个部分:ADC内核,ADC的JESD接口,[color

2017-08-09 20:33:19

DC1974A-C,LTC2122演示板,14位,170Msps双通道ADC,带JESD204B输出。演示电路1974A-C支持具有符合JESD204B标准的CML输出的LTC2122,14位双

2019-06-20 08:05:16

你好,有些身体可以帮助我。我使用ultrascale和jesd204 ip(版本7.0,vivado2016.1),adc芯片是TI的ads54j60,lmfs是8224,子类0,线速率是5Gb

2019-04-24 08:27:05

版中。 问:我为转换器分配的JESD204B通道在系统板上无法顺利路由至FPGA。交叉对太多,非常容易受串扰影响。能否重新映射JESD204B的通道分配,改善布局?答:虽然转换器的JESD204

2018-12-10 09:44:59

嗨, 我尝试在Vivado 2013.4中构建我们的设计并构建Xilinx JESD204B设计示例,我收到以下错误:错误:[Common 17-69]命令失败:此设计包含不支持比特流生成的内核

2018-12-10 10:39:23

作者:Ken C在上篇博客《理解JESD204B协议》中,我对 JESD204B 协议中的三个状态进行了概括性的功能介绍。这三个状态对于在链路的 TX 和 RX 之间构建有效数据链路非常重要,它们

2018-09-13 09:55:26

在上篇博客《理解JESD204B协议》中,我对 JESD204B 协议中的三个状态进行了概括性的功能介绍。这三个状态对于在链路的 TX 和 RX 之间构建有效数据链路非常重要,它们是:代码组同步

2022-11-21 07:18:42

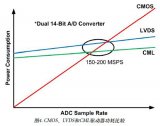

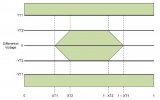

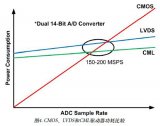

数转换器(ADC)正经历从并行LVDS(低压差分信号)和CMOS数字接口到串行接口(JESD204)的转变。 JESD204标准 自从2006年发布以来,JESD204标准经过两次更新,目前版本为B

2018-12-25 09:27:33

你好,我试图仅在测试模式下测试JESD204B v6.2:001:无限期地发送/接收/K28.5/但首先在desing块中有一个错误:[BD 41-967] AXI接口引脚/ jesd204

2019-04-19 13:06:30

。目前,我在设计中想使用ZYNQ 7015系列的FPGA,利用JESD204 IP核接收A/D转换器AD9683转换完成后的数据。但是JESD204 IP核的端口很多,我不知道应该如何将AD9683

2018-09-05 11:45:31

描述高速多通道应用需要低噪声、可扩展且可进行精确通道间偏斜调节的时钟解决方案,以实现最佳系统 SNR、SFDR 和 ENOB。此参考设计支持在菊链配置中增加 JESD204B 同步时钟。此设计可提供

2018-12-28 11:54:19

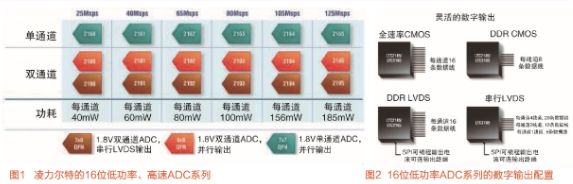

Analog Devices, Inc. (ADI)推出一对支持 JESD204A 数据转换器串行接口标准的低功耗、高速14位 ADC(模数转换器)AD9644 和 AD9641。JESD204A 标准允许高速通信和数据采集系统的设计人员在延长传

2010-08-06 09:29:06 916

916 电子发烧友网讯:目前有一种新型的转换器接口正处于稳步上升的阶段,根据其发展形势,将来它或许会成为首选的转换器协议,那就是JESD204。这种接口在几年前就已经推出了,在经过

2012-08-07 11:48:54 3369

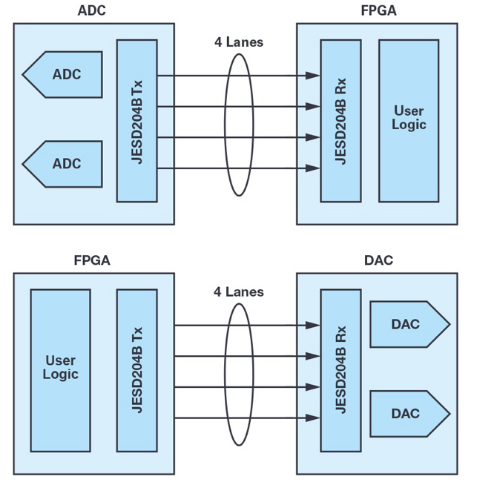

3369 JESD204 LogiCORE™ IP和ADI AD9250模数高速数据转换器之间的JESD204B实现互操作。实现逻辑和数据转换器器件之间的JESD204B互操作性,是促进该新技术广泛运用的一个重大里程碑。

2013-10-09 11:10:34 1956

1956 B Xilinx收发器调试工具,可支持312.5Mbps至12.5Gbps的JESD204B数据转换器至FPGA串行数据接口和Xilinx® Inc., 7系列FPGA及Zynq®-7000全可编程SoC。

2013-10-17 16:35:20 909

909 JESD204B 链路是数据转换器数字接口的最新趋势。这些链路利用高速串行数字技术提供很大的益处(包括增大的信道密度)。此参考设计解决了其中一个采用新接口的挑战:理解并设计链路延迟。一个示例实现

2017-02-08 04:28:02 354

354 简介 JESD204是一种连接数据转换器(ADC和DAC)和逻辑器件的高速串行接口,该标准的 B 修订版支持高达 12.5 Gbps串行数据速率,并可确保 JESD204 链路具有可重复的确定性延迟

2017-04-12 10:22:11 14645

14645

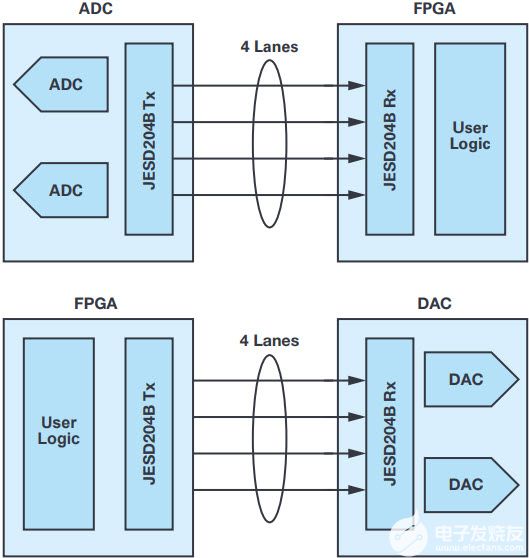

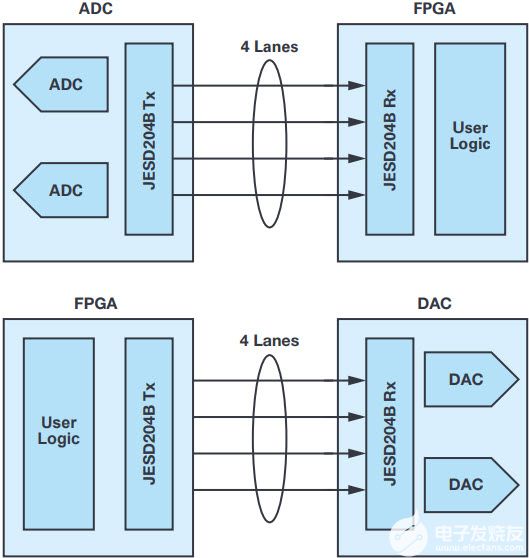

什么是JESD? JESD204B是一种连接数据转换器(ADC和DAC)和逻辑器件的高速串行接口,支持高达12.5 Gbps串行数据速率,并可确保JESD204 链路具有可重复的确定性延迟。在这里

2017-11-15 20:06:01 1575

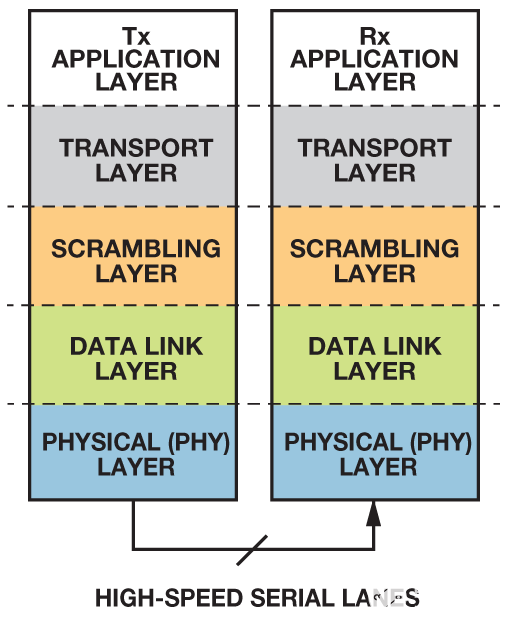

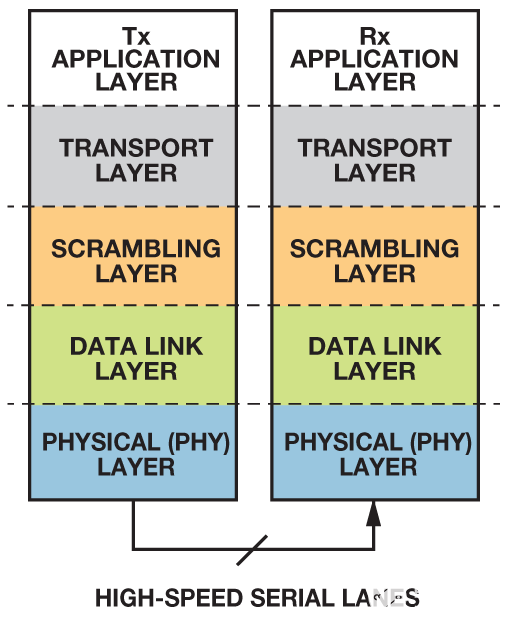

1575 配置更灵活的SDR(软件定义无线电)平台的GSPS ADC,高速串行接口(在此情况下既JESD204B)是必不可少的。JESD204B标准是一种分层规范,了解这一点很重要。规范中的各层都有自己的功能要完成。应用层支持JESD204B链路的配置和数据映射。

2017-11-16 18:48:16 9537

9537

JESD204是一种连接数据转换器(ADC和DAC)和逻辑器件的高速串行接口,该标准的 B 修订版支持高达 12.5 Gbps串行数据速率,并可确保 JESD204 链路具有可重复的确定性延迟。随着

2017-11-17 14:44:16 6595

6595 进而降低输入/输出及电路板面积需求,符合无线通信、量测、国防、航天等应用所需。 一般选择高速模拟数字转换器(ADC)时,ADC延迟高低大多并非重要设计因素或规格,最近新的JESD204B高速串行接口正迅速在全球普及,也逐渐成为数字接口。

2017-11-17 14:45:16 2615

2615

随着转换器分辨率和速度的提高,对于效率更高的接口的需求也随之增长。一种新型转换器接口——JESD204——诞生于几年前,其作为转换器接口经过几次版本更新后越来越受瞩目,效率也更高。如今,该接口

2017-11-18 02:36:14 3196

3196

在从事高速数据撷取设计时使用FPGA的人大概都听过新JEDEC标准「JESD204B」的名号。近期许多工程师均联络德州仪器,希望进一步了解 JESD204B 接口,包括与FPGA如何互动、JESD204B如何让他们的设计更容易执行等。本文介绍 JESD204B标准演进,以及对系统设计工程师有何影响。

2017-11-18 02:57:01 13942

13942 开发串行接口业界标准JESD204A的目的在于解决以高效率且省钱的方式互连最新宽带数据转换器与其他系统IC的问题。其动机在于通过采用可调整高速串行接口,对接口进行标准化,降低数据转换器与其他设备

2017-11-18 07:31:01 2111

2111

规范,以及利用TI 公司的芯片实现其时序要求。 1. JESD204B 介绍 1.1 JESD204B 规范及其优势 JESD204 是基于SerDes 的串行接口标准,主要用于数模转换器和逻辑器件之间

2017-11-18 08:00:01 1831

1831 如果您有接触使用 FPGA 的高速数据采集设计,没准听说过新术语“JESD204B”。 我在工作中看到过很多工程师询问有关 JESD204B 接口的信息以及它如何同 FPGA 协作。他们特别感兴趣

2017-11-18 08:36:01 3155

3155

JESD204B是最新的12.5 Gb/s高速、高分辨率数据转换器串行接口标准。转换器制造商的相关产品已进入市场,并且支持JESD204B标准的产品预计会在不久的将来大量面世。JESD204B接口

2017-11-18 18:57:16 2789

2789

与赛灵思FPGA连接的数据转换器正迅速采用全新JESD204B高速串行链路。要使用该接口格式及协议,设计必须考虑一些基本硬件及时序问题。

2018-07-19 13:51:00 5435

5435

ADC12J4000[2]等。国内相关技术虽然落后于国外,但各高校和科研机构针对不同的应用均做了相关研究,并取得了一定的进展。本文根据JESD204B标准设计了高速串行接口发送端控制层电路,主要包括传输层、数据链路层。通过搭建的硬件仿真平台,验证了控制层电路的正确性,并且其性能也很理想。

2018-08-22 10:18:28 6838

6838

本次研讨会视频将从原始版本到现在的“B”版本简要介绍JESD204标准。此外,还将介绍与JESD204等高速串行接口相关的常见“高性能指标”。研讨会中涉及的话题也适用于使用类似高速串行接口的应用。

2019-07-05 06:19:00 2671

2671 AD9644是一款低功耗、高速14位ADC,集成JESD204A数据转换器串行接口,使设计人员可以扩展传输长度,同时还能改进信号完整性,简化印刷电路板布局。

2019-08-12 06:20:00 2197

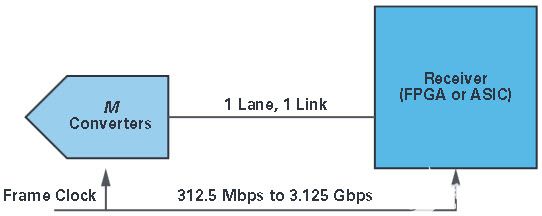

2197 真正的串行接口(称作JESD204)。JESD204 接口被定义为一种单通道、高速串行链路,其使用高达3.125 Gbps 的数据速率把单个或者多个数据转换器连接至数字逻辑器件。

2019-05-13 09:16:42 12564

12564

2006年4月,JESD204最初版本发布。该版本描述了转换器和接收器(通常是FPGA或ASIC)之间数Gb的串行数据链路。在 JESD204的最初版本中,串行数据链路被定义为一个或多个转换器和接收器之间的单串行通道。

2021-01-04 16:27:22 2596

2596

LTC2274:16位、105Msps串行输出ADC(JESD204)数据表

2021-04-28 13:18:42 10

10 LTC2122:带JESD204B串行输出的双14位170 Msps ADC数据表

2021-05-09 21:06:02 11

11 带JESD204B串行接口的14位250 Msps ADC系列

2021-05-18 15:04:50 7

7 LTC2123:带JESD204B串行输出的双14位250 Msps ADC数据表

2021-05-24 08:01:59 8

8 作者:Sureena Gupta

如果您有接触使用 FPGA 的高速数据采集设计,没准听说过新术语“JESD204B”。

我在工作中看到过很多工程师询问有关 JESD204B 接口的信息以及

2021-11-10 09:43:33 528

528

JESD204是JEDEC为了满足对转换器速度和分辨率不断增长的需求而提出的一项新标准,主要描述了一种新的高效串行接口来处理数据转换器。2006 年,JESD204 标准通过多个标准修订版为单通道

2022-02-23 09:24:12 1123

1123 本文余下篇幅将探讨推动该规范发展的某些关键的终端系统应用,以及串行低压差分信号(LVDS)和JESD204B的对比。

2022-08-05 14:18:00 1105

1105

以下是您需要了解的关于 JESD204 串行接口规范第四版的内容

2022-08-12 15:04:02 991

991

由于高速ADC的迅速发展,传输速率已经迈入GSPS,因此JESD204B标准协议将会成为应用范围最广的接口传输协议。

2022-09-05 09:21:15 1465

1465 一个新的转换器接口正在稳步发展,并有望成为未来转换器的首选协议。这个新接口JESD204最初是在几年前推出的,但经过了修订,使其成为更具吸引力和效率的转换器接口。随着转换器分辨率和速度的提高,对更高效接口的需求也在增长。

2022-12-21 14:37:04 2780

2780

JESD204A/JESD204B串行接口行业标准旨在解决以高效和节省成本的方式将最新的宽带数据转换器与其他系统IC互连的问题。其动机是标准化接口,通过使用可扩展的高速串行接口,减少数据转换器与其他设备(如现场可编程门阵列(FGPA)和片上系统(SoC))设备)之间的数字输入/输出数量。

2022-12-21 14:44:20 966

966

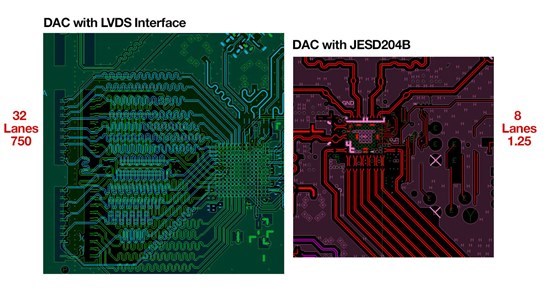

JESD204B接口一般用在高速的AD和DA芯片上,用于传输采集到的数据。该接口相比LVDS可以减少大量的IO管脚,所以正在逐步取代LVDS接口(引用wp446-jesd204b.pdf)。

2022-12-22 09:45:18 1774

1774 JESD204是一款高速串行接口,用于将数据转换器(ADC和DAC)连接到逻辑器件。该标准的修订版B支持高达12.5 Gbps的串行数据速率,并确保JESD204链路上的可重复确定性延迟。随着转换器速度和分辨率的不断提高,JESD204B接口在ADI公司的高速转换器和集成RF收发器中变得越来越普遍。

2023-01-09 16:41:38 2969

2969

High-speedserialinterfaceJESD204接口JESD204标准专用于通过串行接口传输转换器样本。2006年,JESD204标准支持单通道上的多个数据转换器。以下修订版

2022-05-24 16:42:20 658

658

LogiCORE IP JESD204内核实现了一个JESD204B接口,使用GTX、GTH、GTP或GTY(仅限UltraScale和UltraScale+)收发器在1至8个通道上支持1至12.5

2023-10-16 10:57:17 358

358

电子发烧友网为你提供ADI(ADI)AD9207: 12-Bit, 6 GSPS, JESD204B/JESD204C Dual ADC Data Sheet相关产品参数、数据手册,更有AD9207

2023-10-16 19:02:55

电子发烧友App

电子发烧友App

评论